|

Why Gladiator CLD?

|

Dear Customers,

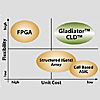

Leopard Logic introduces the Gladiator™ CLD™ family of configurable logic devices. Gladiator CLD combines FPGA flexibility and time to market with ASIC efficiency in a 100% user customizable device. This unique combination delivers superior performance and low power consumption with the lowest total cost of ownership!

Demanding applications in markets such as networking, storage and wireless infrastructure require efficient and flexible implementation platforms. Traditional FPGAs and ASICs cannot meet these requirements due to performance limitations, high power and long time-to- market.

The Next Generation Configurable Logic Device

The Gladiator CLD family consists of five devices with capacities ranging up to 25M system gates and 10Mb of on-chip memory supporting clock speeds of 500MHz. Not limited by pre-defined functionality, Gladiator becomes a customer or market segment specific device by implementing substantial amounts of high-speed logic in the mask-programmable (MP) section of the device. Further customization is achieved by programming the field-programmable (FP) fabric, which allows for an unlimited number of reconfigurations by simply downloading a new bitstream into the device, thus offering optimal in-field programmability. The MP and FP fabrics share a unified core cell architecture, allowing for simple partitioning and full automation by Leopard Logic's design flow. The Gladiator CLD family consists of five devices with capacities ranging up to 25M system gates and 10Mb of on-chip memory supporting clock speeds of 500MHz. Not limited by pre-defined functionality, Gladiator becomes a customer or market segment specific device by implementing substantial amounts of high-speed logic in the mask-programmable (MP) section of the device. Further customization is achieved by programming the field-programmable (FP) fabric, which allows for an unlimited number of reconfigurations by simply downloading a new bitstream into the device, thus offering optimal in-field programmability. The MP and FP fabrics share a unified core cell architecture, allowing for simple partitioning and full automation by Leopard Logic's design flow.

Read the full story...

|

|

Today's Design Dilemma |

|

|

Changing Standards: Technical standards such as communication protocols, data formats or bus interfaces are in a constant state of flux. Rapidly evolving specifications and changing market requirements cause invariable interoperability challenges. Designers have to address these changing requirements under stringent budget constraints, while having to meet ever shortening product development cycles. Changing Standards: Technical standards such as communication protocols, data formats or bus interfaces are in a constant state of flux. Rapidly evolving specifications and changing market requirements cause invariable interoperability challenges. Designers have to address these changing requirements under stringent budget constraints, while having to meet ever shortening product development cycles.

Increasing Costs: Rapidly increasing mask costs and lengthening design cycles of ASICs necessitate new solutions to produce custom logic devices on-time and on-budget. This dilemma is driving the FPGA market today and has caused a resurgence of gate-array style devices that are now being marketed as "Structured ASICs". As fewer companies can afford cell-based ASIC designs, they revert to less-costly options or try to replace custom logic devices with off-the-shelf ASSPs.

Elusive Time to Volume: Today's fast changing market place requires rapid product deployment in order to remain competitive. Latest statistics show that about 50% of ASICs never exceed 100k lifetime units and pinpoint the median design complexity at about 1.2M gates (800k logic and 400k memory). Many ASICs take so long to build that the specifications are outdated by the time the devices are finally delivered, thus rendering them practically obsolete. On the other hand, while quick to market, FPGAs are not suitable for high- volume deployment. The result is a growing number of system designers seeking viable alternatives to implement their logic designs. Elusive Time to Volume: Today's fast changing market place requires rapid product deployment in order to remain competitive. Latest statistics show that about 50% of ASICs never exceed 100k lifetime units and pinpoint the median design complexity at about 1.2M gates (800k logic and 400k memory). Many ASICs take so long to build that the specifications are outdated by the time the devices are finally delivered, thus rendering them practically obsolete. On the other hand, while quick to market, FPGAs are not suitable for high- volume deployment. The result is a growing number of system designers seeking viable alternatives to implement their logic designs.

Learn More... »

|

|

|

Reasons to use Gladiator CLD |

|

|

Unmatched Capability: Gladiator CLD is the first device on the market that combines ASIC and FPGA technology in a single device. Because of the integrated FPGA blocks, Gladiator CLD retains the ability to update devices during debug but also in the field by simply downloading a new configuration bitstream.

High Performance: The internal clock networks are designed for clock speeds up to 500MHz under worst case conditions. A Gladiator CLD device consumes only about 1/4 of the power of an FPGA running the same design. Gladiator CLD also eliminates the notorious power-on glitch of FPGAs.

Fast Time to Market: Once a designer has synthesized the design and produced the configuration data, samples can be delivered within 4 weeks. The low upfront NRE combined with the efficient implementation make Gladiator CLD the most cost-effective solution in the unit volume range between 1k to 100k units.

See it for yourself - schedule your evaluation today! »

|

| Quick Links... |

|

|

![]()