## Outline

## Sequential Statements

- 1. VHDL process

- 2. Sequential signal assignment statement

- 3. Variable assignment statement

- 4. If statement

- 5. Case statement

- 6. Simple for loop statement

| RTL Hardware Design<br>by P. Chu | Chapter 5 | 1 | RTL Hardware Design<br>by P. Chu | Chapter 5 | 2 |

|----------------------------------|-----------|---|----------------------------------|-----------|---|

|                                  |           |   | -,                               |           |   |

3

5

## 1. VHDL Process

- Contains a set of sequential statements to be executed sequentially

- · The whole process is a concurrent statement

- Can be interpreted as a circuit part enclosed inside of a black box

- May or may not be able to be mapped to physical hardware

| RTL Hardware Design |  |

|---------------------|--|

| by P. Chu           |  |

Chapter 5

- · Two types of process

- A process with a sensitivity list

- A process with wait statement

RTL Hardware Design by P. Chu Chapter 5

4

6

## A process with a sensitivity list

- Syntax

- process(sensitivity\_list) declarations; begin

- sequential statement; sequential statement;

...

#### end process;

RTL Hardware Design Chapter 5 by P. Chu

- A process is like a circuit part, which can be

- active (known activated)

- inactive (known as *suspended*).

- A process is activated when a signal in the sensitivity list changes its value

- Its statements will be executed sequentially until the end of the process

RTL Hardware Design by P. Chu Chapter 5

- E.g, 3-input and circuit signal a,b,c,y: std\_logic; process(a,b,c) begin y <= a and b and c; end process;

- How to interpret this: process(a) begin y <= a and b and c; end process;

• For a combinational circuit, all input should be included in the sensitivity list

RTL Hardware Design Chapter 5 by P. Chu

## A process with wait statement

- · Process has no sensitivity list

- Process continues the execution until a wait statement is reached and then suspended

- · Forms of wait statement:

- wait on signals;

- wait until boolean\_expression;

- wait for time\_expression;

RTL Hardware Design by P. Chu

7

9

E.g, 3-input and circuit process begin y <= a and b and c; wait on a, b, c; end process;

RTL Hardware Design by P. Chu

- · A process can has multiple wait statements

- Process with sensitivity list is preferred for synthesis

Chapter 5

```

• E.g.,

process(a,b,c,d)

begin

-- y_{entry} := y

-- y<sub>exit</sub> := a or c;

y <= a or c;

y <= a and b;

-- y<sub>exit</sub> := a and b;

-- y<sub>exit</sub> := c and d;

y <= c and d;

-- y <= y<sub>exit</sub>

end process;

• It is same as

process(a,b,c,d)

begin

y <= c and d;

end process;

What happens if the 3 statements are concurrent

statements?

```

RTL Hardware Design Chapter 5 11 by P. Chu

# 2. Sequential signal assignment statement

Chapter 5

8

10

12

- Syntax signal\_name <= value\_expression;</li>

- Syntax is identical to the simple concurrent signal assignment

- Caution:

- Inside a process, a signal can be assigned multiple times, but only the last assignment takes effect

Chapter 5

RTL Hardware Design by P. Chu

## 3. Varible assignment statement

- Syntax

- variable\_name := value\_expression;

- · Assignment takes effect immediately

- No time dimension (i.e., no delay)

- Behave like variables in C

- Difficult to map to hardware (depending on context)

• E.g., process(a,b,c) variable tmp: std\_logic; begin tmp := '0'; tmp := tmp or a; tmp := tmp **or** b; y <= tmp; end process;

• interpretation: process(a,b,c) variable tmp0, tmp1, tmp2: std\_logic; begin tmp0 := '0'; tmp1 := tmp0 **or** a; tmp2 := tmp1 **or** b; y <= tmp2; end process; tmp0 '0' tmp1 а tmp2 b RTL Hardware Design by P. Chu Chapter 5

• What happens if signal is used? process(a,b,c,tmp) begin -- tmp<sub>entry</sub> := tmp tmp <= '0'; -- tmp<sub>exit</sub> := '0'; tmp <= tmp **or** a; -- tmp<sub>exit</sub> := tmp<sub>entry</sub> **or** a;  $tmp \le tmp \text{ or } b; -- tmp_{exit} := tmp_{entry} \text{ or } b;$ -- tmp <= tmp<sub>exit</sub> end process; · Same as: process(a,b,c,tmp) begin tmp <= tmp **or** b; end process; Chapter 5

Chapter 5

#### RTL Hardware Design by P. Chu

RTL Hardware Design by P. Chu

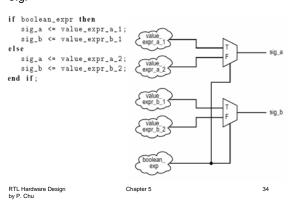

#### 4. IF statement

Syntax

13

15

17

- · Examples

- · Comparison to conditional signal assignment

- Incomplete branch and incomplete signal assignment

Chapter 5

• Conceptual Implementation

RTL Hardware Design by P. Chu

16

14

## **Syntax**

if boolean\_expr\_1 then sequential\_statements; elsif boolean\_expr\_2 then sequential\_statements; elsif boolean\_expr\_3 then sequential\_statements;

#### . . . else

sequential\_statements; end if;

RTL Hardware Design by P. Chu Chapter 5

## E.g., 4-to-1 mux

architecture if\_arch of mux4 is begin

| 0                                |                 |       |        |

|----------------------------------|-----------------|-------|--------|

| process (a, b                    | ,c,d,s)         |       |        |

| begin                            |                 |       |        |

| if (s="00                        | O") then        |       |        |

| x <= ;                           | a;              |       |        |

| elsif (s=                        | = " 01 " ) then | input | output |

| x <= 1                           | b;              | s     | x      |

| elsif (s:                        | = " 10 " ) then |       |        |

| x <= (                           | c;              | 0.0   | a      |

| else                             |                 | 0 1   | b      |

| x <= 0                           | d;              | 10    | С      |

| end if;                          |                 | 11    | d      |

| end process                      | ;               |       |        |

| <pre>end if_arch;</pre>          |                 |       |        |

| RTL Hardware Design<br>by P. Chu | Chapter 5       |       | 18     |

## E.g., 2-to-2<sup>2</sup> binary decoder

| architecture if_arch of dec<br>begin       | oder4 | i s    |

|--------------------------------------------|-------|--------|

| process (s)                                |       |        |

| begin                                      |       |        |

| if (s="00") then                           |       |        |

| x <= "0001";                               | input | output |

| elsif (s="01") then                        | s     | х      |

| x <= "0010";                               |       | 0001   |

| elsif (s="10")then                         | 0 0   | 0001   |

| x <= "0100";                               | 0 1   | 0010   |

| else                                       | 10    | 0100   |

| x <= "1000";                               | 11    | 1000   |

| end if;                                    | 11    | 1000   |

| end process;                               | -     |        |

| <pre>end if_arch;</pre>                    |       |        |

| RTL Hardware Design Chapter 5<br>by P. Chu |       | 19     |

#### E.g., 4-to-2 priority encoder

architecture if\_arch of prio\_encoder42 is begin process(r) \_\_\_\_\_

| process(1)                                 |                 |       |        |

|--------------------------------------------|-----------------|-------|--------|

| begin                                      | input           | outp  | ut     |

| if (r(3)='1') then                         | r               | code  | active |

| code <= "11";<br>elsif (r(2)='1')then      | 1               | 11    | 1      |

| code <= "10";                              | $0 \ 1$         | 10    | 1      |

| elsif (r(1)='1') then                      | 001-            | 01    | 1      |

| code <= "01";                              | $0 \ 0 \ 0 \ 1$ | 00    | 1      |

| else                                       | 0000            | 00    | 0      |

| code <= "00";                              |                 |       |        |

| end if;                                    |                 |       |        |

| end process;                               |                 |       |        |

| active <= r(3) or r(2) or                  | r(1) (          | or r( | 0);    |

| end if_arch;                               |                 |       |        |

| RTL Hardware Design Chapter 5<br>by P. Chu |                 |       | 20     |

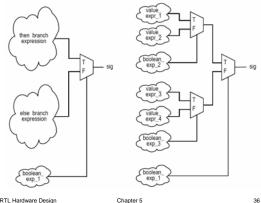

## Comparison to conditional signal assignment

- Two statements are the same if there is only one output signal in if statement

- If statement is more flexible

- Sequential statements can be used in then, elsif and else branches:

- Multiple statements

- Nested if statements

| RTL Hardware Design | Chapter 5 |

|---------------------|-----------|

| by P. Chu           |           |

#### sig <= value\_expr\_1 when boolean\_expr\_1 else value\_expr\_2 when boolean\_expr\_2 else value\_expr\_3 when boolean\_expr\_3 else ...value\_expr\_n; It can be written as process(...) if boolean\_expr\_1 then sig <= value\_expr\_1; elsif boolean\_expr\_2 then sig <= value\_expr\_2; elsif boolean\_expr\_3; .... else

```

sig <= value_expr_n;

end if;

end process

RTL Hardware Design Chapter 5 22

by P. Chu

```

#### e.g., find the max of a, b, c

```

if (a > b) thensignal ac_max, beif (a > c) thena > cmax <= a;--a > b and a > celseac_max <= a whenmax <= c;--a > b and c >= aend if;max <= c;max <= b;--b >= a and b > cmax <= c;--b >= a and c >= bmax <= c;--b >= amax <= c;max <= c;<

```

21

| RTL Hardware Design | Chapter 5 | 23 |

|---------------------|-----------|----|

| by P. Chu           |           |    |

#### e.g., 2 conditional sig assignment codes

| signal                       | ac_max, bc_max: std_logic;                                                                    |    |

|------------------------------|-----------------------------------------------------------------------------------------------|----|

| bc_max                       | <= a when (a > c) else c;<br><= b when (b > c) else c;<br>ac_max when (a > b) else bc_max;    |    |

| max <=                       | a when $((a > b)$ and $(a > c))$ else<br>c when $(a > b)$ else<br>b when $(b > c)$ else<br>c; | 5  |

| RTL Hardware De<br>by P. Chu | sign Chapter 5                                                                                | 24 |

• 2 conditional sig assign implementations

```

signal ac_max, bc_max: std_logic;

....

ac_max <= a when (a > c) else c;

bc_max <= b when (b > c) else c;

max <= ac_max when (a > b) else bc_max;

max <= a when ((a > b) and (a > c)) else

c when (a > b) else

b when (b > c) else

c;

RTL Hardware Design

by P. Chu

```

#### e.g., "sharing" boolean condition

```

if (a > b and op="00") then

y <= a - b;

z <= a - 1;

status <= '0';

else

y <= b - a;

z <= b - 1;

status <= '1';

end if;

</pre>

```

Incomplete branch and incomplete

26

|                                                              | signal assignment                                                                                                          |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| $y \le a-b$ when $(a > b$ and $op="00")$ else                | <ul> <li>According to VHDL definition:</li> </ul>                                                                          |

| b-a;<br>z <= a-1 when (a > b and op="00") else<br>b-1;       | <ul> <li>Only the "then" branch is required; "elsif" and<br/>"else" branches are optional</li> </ul>                       |

| <pre>status &lt;= '0' when (a &gt; b and op="00") else</pre> | <ul> <li>Signals do not need to be assigned in all<br/>branch</li> </ul>                                                   |

|                                                              | <ul> <li>When a signal is unassigned due to omission,<br/>it keeps the "previous value" (implying<br/>"memory")</li> </ul> |

| RTL Hardware Design Chapter 5 27<br>by P. Chu                | RTL Hardware Design Chapter 5 28<br>by P. Chu                                                                              |

## Incomplete branch

| -                                                                                                      |                                                                                                                                          | • fix                                                                                                 |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| <pre>• E.g., process(a,b) begin     if (a=b) then         eq &lt;= '1';     end if; end process;</pre> | <pre>• It implies process(a,b) begin     if (a=b) then         eq &lt;= '1';     else         eq &lt;= eq;     end if; end process</pre> | process(a,b)<br>begin<br>if (a=b) then<br>eq <= '1';<br>else<br>eq <= '0';<br>end if ;<br>end process |

| RTL Hardware Design | Chapter 5 | 29 | RTL Hardware Design | Chapter 5 | 30 |

|---------------------|-----------|----|---------------------|-----------|----|

| by P. Chu           |           |    | by P. Chu           |           |    |

```

Incomplete signal assignment

process (a,b)

```

```

• E.g.,

begin

if (a>b) then

gt <= '1';

elsif (a=b) then

eq <= '1';

else

lt <= '1';

end if;

end process;

```

RTL Hardware Design by P. Chu

```

• Fix #1:

• Fix #2

process (a,b)

process (a,b)

begin

begin

if (a>b) then

gt <= '0';

eq <= `0';

lt <= `0';

gt <= '1';

eq <= '0';

lt <= '0';

if (a>b) then

elsif (a=b) then

gt <= '1';

gt <= '0';

elsif (a=b) then

eq <= '1';

eq <= '1';

lt <= '0';

else

else

lt <= '1';

gt <= '0';

end if;

eq <= '0';

end process;

lt <= '1';

end if;

end process;

RTL Hardware Design

by P. Chu

Chapter 5

32

```

## Conceptual implementation

Chapter 5

- · Same as conditional signal assignment statement if the if statement consists of

- One output signal

- One sequential signal assignment in each branch

- Multiple sequential statements can be constructed recursively

| RTL Hardware Design | Chapter 5 |

|---------------------|-----------|

| by P. Chu           |           |

```

e.g. if boolean_expr_1 then

if boolean_expr_2 then

signal_a <= value_expr_1;</pre>

else

signal_a <= value_expr_2;</pre>

end if;

else

if boolean_expr_3 then

signal_a <= value_expr_3;

e l s e

signal_a <= value_expr_4;</pre>

end if;

end if;

```

| RTL Hardware Design | Chapter 5 |

|---------------------|-----------|

| by P. Chu           |           |

31

33

35

#### 5. Case statement

- Syntax

- Examples

- · Comparison to selected signal assignment statement

- Incomplete signal assignment

- Conceptual Implementation

| RTL Hardware Design<br>by P. Chu | Chapter 5 | 37 |

|----------------------------------|-----------|----|

## **Syntax**

case case\_expression is when choice\_1 => sequential statements; when choice\_2 => sequential statements; . . . when choice\_n => sequential statements; end case; Chapter 5

RTL Hardware Design by P. Chu

## E.g., 4-to-1 mux

| architecture case_arch<br>begin<br>process(a,b,c,d,s) | of mux4   | is |       |        |

|-------------------------------------------------------|-----------|----|-------|--------|

| begin                                                 |           |    |       |        |

| case s is                                             |           |    | input | output |

| when "00" =><br>x <= a;                               |           |    | s     | x      |

| when "01" =><br>x <= b;                               |           |    | 0.0   | a      |

| when "10" =>                                          |           |    | 01    | b      |

| x <= c;                                               |           |    | 10    | С      |

| when others =><br>x <= d;                             |           |    | 11    | d      |

| end case;                                             |           |    |       |        |

| end process;<br>end case_arch;                        |           |    |       |        |

| RTL Hardware Design<br>v P. Chu                       | Chapter 5 |    |       |        |

#### E.g., 4-to-2 priority encoder

39

| begin        |                         |       |              |       |

|--------------|-------------------------|-------|--------------|-------|

| case r is    |                         |       |              |       |

| when "100    | 0" "1001" "1010" "1011' | 1     |              |       |

| " 110        | 0" "1101" "1110" "1111' | =>    |              |       |

| code <       | = "11":                 |       |              |       |

| when "010    | 0" "0101" "0110" "0111" | = >   |              |       |

| code <       | = "10";                 |       |              |       |

| when "001    | 0" "0011" =>            | input | outp<br>code | activ |

| code <       | = "01";                 |       |              | activ |

| when othe    | rs =>                   | 1     | 11           | 1     |

| code <       | = "00";                 | 01    |              | 1     |

| end case;    | ,                       | 0001- |              | 1     |

|              |                         | 0000  | ~ ~          | ò     |

| end process; |                         |       |              |       |

## E.g., 2-to-2<sup>2</sup> binary decoder

38

40

42

| <b>0</b> /                                 |       |        |

|--------------------------------------------|-------|--------|

| architecture case_arch of decoder4 is      | 5     |        |

| begin                                      |       |        |

| proc1:                                     |       |        |

| process (s)                                |       |        |

| begin                                      | input | output |

| case s is                                  | s     | x      |

| when "00" =>                               |       |        |

| x <= "0001";                               | 0.0   | 0001   |

| when "01" =>                               | 0.1   | 0010   |

| x <= "0010";                               | 10    | 0100   |

| when "10" =>                               | 11    | 1000   |

| x <= "0100";                               |       | 1000   |

| when others =>                             |       |        |

| x <= "1000";                               |       |        |

| end case;                                  |       |        |

| end process;                               |       |        |

| END case_arch;                             |       |        |

| RTL Hardware Design Chapter 5<br>by P. Chu |       |        |

#### Comparison to selected signal assignment

- Two statements are the same if there is only one output signal in case statement

- · Case statement is more flexible

- · Sequential statements can be used in choice branches

RTL Hardware Design by P. Chu

Chapter 5

| value_                                                                                                                                                                                                                    | ect<br>expr_1 when chose<br>expr_2 when chose<br>expr_3 when chose      | ice_2, | Incomplete                       | e signal assigr      | iment   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------|----------------------------------|----------------------|---------|

| <pre>lt can be rewritten as:<br/>case sel_exp is<br/>when choice_1<br/>sig &lt;= val<br/>when choice_2<br/>sig &lt;= val<br/>when choice_3<br/>sig &lt;= val<br/><br/>when choice_n<br/>sig &lt;= val<br/>end case;</pre> | <pre>ue_expr_1;<br/>=&gt;<br/>ue_expr_2;<br/>=&gt;<br/>ue_expr_3;</pre> | ice_n; | choice branch<br>– When a signa  | t need to be assigne | eps the |

| RTL Hardware Design<br>by P. Chu                                                                                                                                                                                          | Chapter 5                                                               | 43     | RTL Hardware Design<br>by P. Chu | Chapter 5            | 44      |

Incomplete signal assignment

```

• E.g.,

process(a)

case a is

when "100"|"101"|"110"|"111" =>

high <= '1';

when "010"|"011" =>

middle <= '1';

when others =>

low <= '1';

end case;

end process;

</pre>

```

```

RTL Hardware Design Chapter 5 46

by P. Chu

```

```

• Fix #2:

process(a)

high <= '0';

middle <= '0';

low <= '0';

case a is

when "100"|"101"|"110"|"111" =>

high <= '1';

when "010"|"011" =>

middle <= '1';

when others =>

low <='1';

end case;

end process;

```

| RTL Hardware Design | Chapter 5 |

|---------------------|-----------|

| by P. Chu           |           |

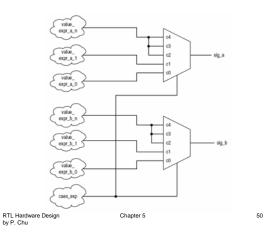

## Conceptual implementation

- Same as selected signal assignment statement if the case statement consists of

- One output signal

- One sequential signal assignment in each branch

Chapter 5

• Multiple sequential statements can be constructed recursively

RTL Hardware Design by P. Chu

47

48

```

e.g.

case case_exp is

when c0 =>

sig_a <= value_expr_a_0;

sig_b <= value_expr_b_0;

when c1 =>

sig_a <= value_expr_a_1;

sig_b <= value_expr_b_1;

when others =>

sig_a <= value_expr_a_n;

sig_b <= value_expr_b_n;

end case;</pre>

```

#### 6. Simple for loop statement

Chapter 5

Chapter 5

49

51

Syntax

RTL Hardware Design by P. Chu

RTL Hardware Design by P. Chu

- Examples

- Conceptual Implementation

| ٠ | VHDL | provides | а | variety | of | loop | constructs |

|---|------|----------|---|---------|----|------|------------|

|---|------|----------|---|---------|----|------|------------|

- Only a restricted form of loop can be synthesized

- Syntax of simple for loop: for index in loop\_range loop sequential statements;

- end loop;

- loop\_range must be static

- Index assumes value of loop\_range from left to right

Chapter 5

52

54

RTL Hardware Design by P. Chu

#### • E.g., bit-wide xor

```

library ieee;

use ieee.std_logic_1164.all;

entity wide_xor is

port(

a, b: in std_logic_vector(3 downto 0);

y; out std_logic_vector(3 downto 0)

);

end wide_xor;

architecture demo_arch of wide_xor is

constant WIDTH: integer := 4;

begin

process(a, b)

begin

for i in (WIDTH-1) downto 0 loop

y(i) <= a(i) xor b(i);

end loop;

end process;

end demo_arch;

RTL Hardware Design Chapter 5 53

byP.Chu

```

#### • E.g., reduced-xor

## Conceptual implementation

- "Unroll" the loop

- For loop should be treated as "shorthand" for repetitive statements

- E.g., bit-wise xor

RTL Hardware Design by P. Chu

| y(3) | <= | a(3) | xor | b(3); |

|------|----|------|-----|-------|

| y(2) | <= | a(2) | xor | b(2); |

| y(1) | <= | a(1) | xor | b(1); |

| y(0) | <= | a(0) | xor | b(0); |

Chapter 5

• E.g., reduced-xor

```

tmp(0) <= a(0);

tmp(1) <= a(1) xor tmp(0);

tmp(2) <= a(2) xor tmp(1);

tmp(3) <= a(3) xor tmp(2);

y <= tmp(3);</pre>

```

Chapter 5

56

58

## Synthesis of sequential statements

- Concurrent statements

- Modeled after hardware

- Have clear, direct mapping to physical structures

- Sequential statements

- Intended to describe "behavior"

- Flexible and versatile

- Can be difficult to be realized in hardware

Chapter 5

- Can be easily abused

RTL Hardware Design by P. Chu

57

55

• Think hardware

RTL Hardware Design by P. Chu

Designing hardware is not converting a C program to a VHDL program

Chapter 5

RTL Hardware Design by P. Chu