# Concurrent Signal Assignment Statements

#### **Outline**

- 1. Combinational versus sequential circuit

- 2. Simple signal assignment statement

- 3. Conditional signal assignment statement

- 4. Selected signal assignment statement

- 5. Conditional vs. selected signal assignment

### 1. Combinational vs. sequential circuit

- Combinational circuit:

- No internal state

- Output is a function of inputs only

- No latches/FFs or closed feedback loop

- Sequential circuit:

- With internal state

- Output is a function of inputs and internal state

- Sequential circuit to be discussed later

# 2. Simple signal assignment statement

- Simple signal assignment is a special case of conditional signal assignment

- Syntax:

signal\_name <= projected\_waveform;</li>

- E.g.,

y <= a + b + 1 after 10 ns;</li>

- Timing info ignored in synthesis and δ-delay is used: signal name <= value expression</li>

```

E.g.,

status <= '1';

even <= (p1 and p2) or (p3 and p4);

arith_out <= a + b + c - 1;</li>

```

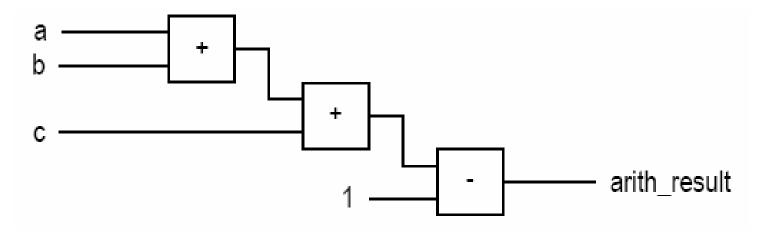

Implementation of last statement

# Signal assignment statement with a closed feedback loop

- a signal appears in both sides of a concurrent assignment statement

- E.g.,

q <= ((not q) and (not en)) or (d and en);</li>

- Syntactically correct

- Form a closed feedback loop

- Should be avoided

# 3. Conditional signal assignment statement

- Syntax

- Examples

- Conceptual implementation

- Detailed implementation examples

# Syntax

Simplified syntax:

```

signal_name

<= value_expr_1 when boolean_expr_1 else

value_expr_2 when boolean_expr_2 else

value_expr_3 when boolean_expr_3 else

...

value_expr_n</pre>

```

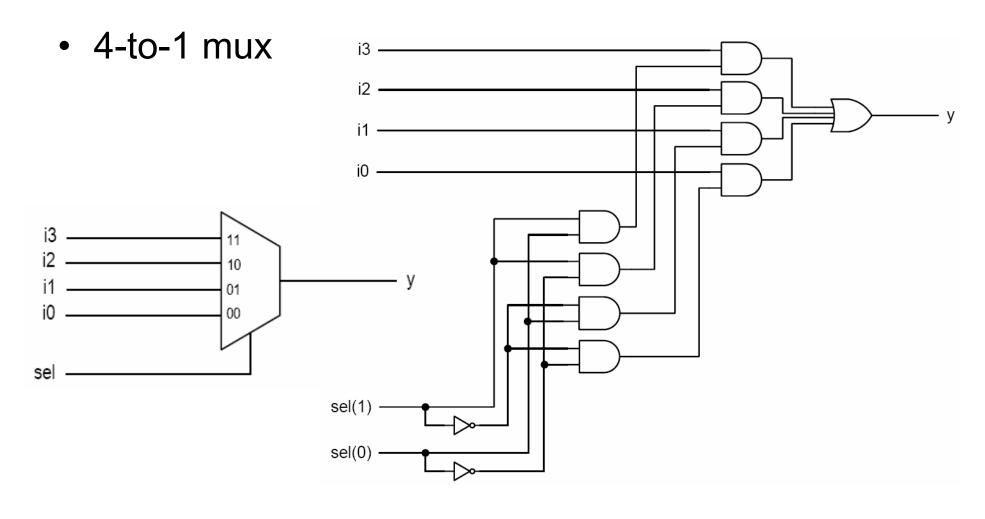

# E.g., 4-to-1 mux

| input | output |

|-------|--------|

| s     | Х      |

| 0 0   | a      |

| 0.1   | b      |

| 10    | С      |

| 1 1   | d      |

```

library ieee;

use ieee.std_logic_1164.all;

entity mux4 is

port (

a,b,c,d: in std_logic_vector(7 downto 0);

s: in std_logic_vector(1 downto 0);

x: out std_logic_vector(7 downto 0)

);

end mux4;

architecture cond_arch of mux4 is

begin

x \le a \text{ when } (s="00") \text{ else}

b when (s="01") else

c when (s="10") else

d;

end cond_arch;

```

# E.g., 2-to-2<sup>2</sup> binary decoder

| input | output |

|-------|--------|

| S     | X      |

| 0 0   | 0001   |

| 0 1   | 0010   |

| 1 0   | 0100   |

| 1 1   | 1000   |

```

library ieee;

use ieee.std_logic_1164.all;

entity decoder4 is

port (

s: in std_logic_vector(1 downto 0);

x: out std_logic_vector(3 downto 0)

);

end decoder4;

architecture cond_arch of decoder4 is

begin

x \le "0001" when (s="00") else

"0010" when (s="01") else

"0100" when (s="10") else

"1000":

end cond_arch;

```

# E.g., 4-to-2 priority encoder

| input        | output |        |

|--------------|--------|--------|

| r            | code   | active |

| 1            | 11     | 1      |

| 01           | 10     | 1      |

| 0 0 1 -      | 01     | 1      |

| $0\ 0\ 0\ 1$ | 00     | 1      |

| 0000         | 00     | 0      |

```

library ieee;

use ieee.std_logic_1164.all;

entity prio_encoder42 is

port (

r: in std_logic_vector(3 downto 0);

code: out std_logic_vector(1 downto 0);

active: out std_logic

);

end prio_encoder42;

architecture cond_arch of prio_encoder42 is

begin

code \leq "11" when (r(3)='1') else

"10" when (r(2)='1') else

"01" when (r(1)='1') else

"00":

active \leftarrow r(3) or r(2) or r(1) or r(0);

end cond_arch ;

```

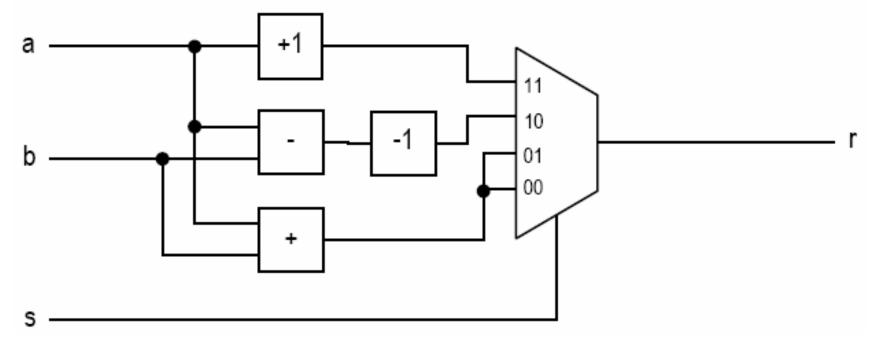

# E.g., simple ALU

| <b>input</b> | <b>output</b>        |

|--------------|----------------------|

| ctrl         | result               |

| 0            | src0 + 1             |

| 1 0 0        | src0 + src1          |

| 1 0 1        | src0 - src1          |

| 1 1 0        | src0 <b>and</b> src1 |

| 111          | src0 <b>or</b> src1  |

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity simple_alu is

port (

ctrl: in std_logic_vector(2 downto 0);

src0, src1: in std_logic_vector(7 downto 0);

result: out std_logic_vector(7 downto 0)

);

end simple_alu ;

architecture cond_arch of simple_alu is

signal sum, diff, inc: std_logic_vector(7 downto 0);

begin

inc <= std_logic_vector(signed(src0)+1);</pre>

sum <= std_logic_vector(signed(src0)+signed(src1));</pre>

diff <= std_logic_vector(signed(src0)-signed(src1));</pre>

result <= inc when ctrl(2)='0' else

sum when ctrl(1 downto 0)="00" else

diff when ctrl(1 downto 0)="01" else

src0 and src1 when ctrl(1 downto 0)="10" else

src0 or src1;

end cond_arch;

RTL Hardware Design

Chapter 4

```

17

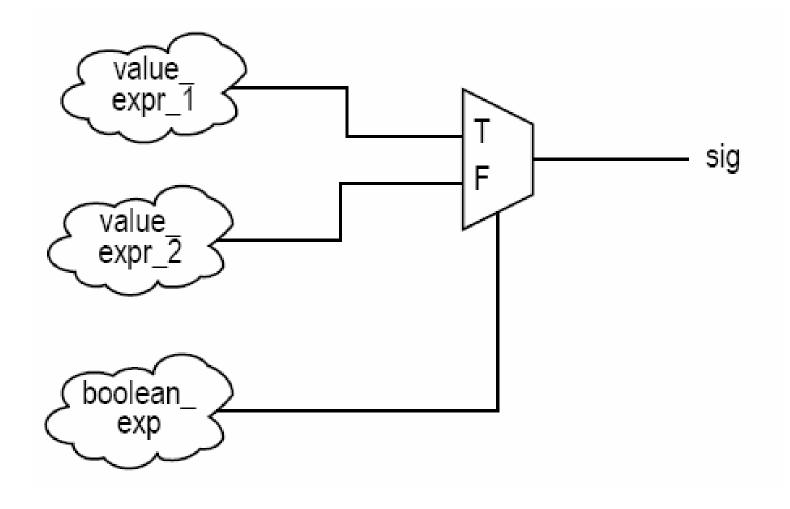

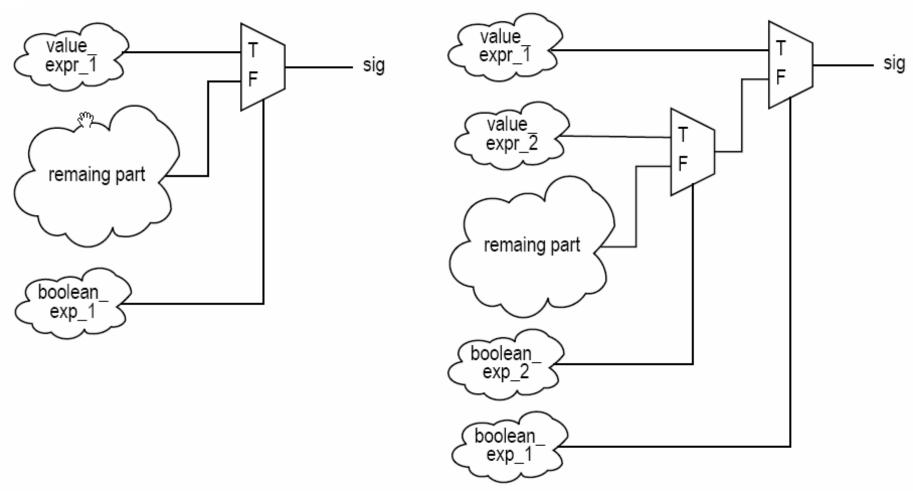

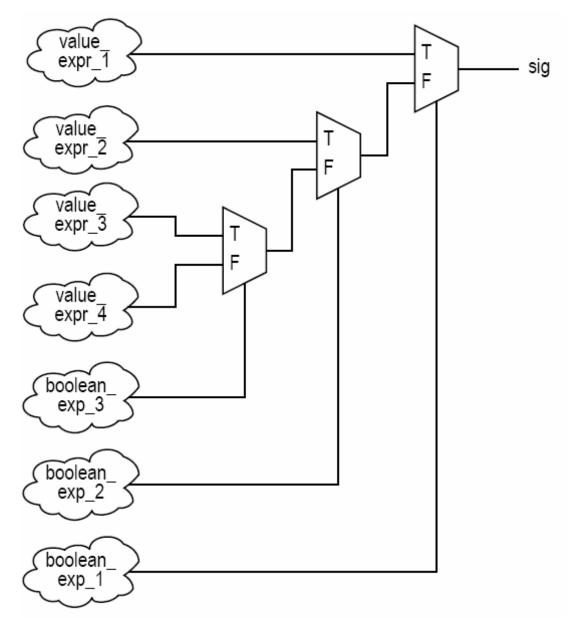

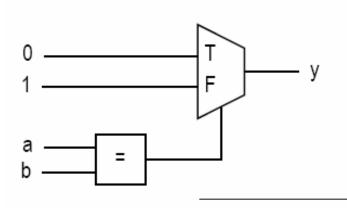

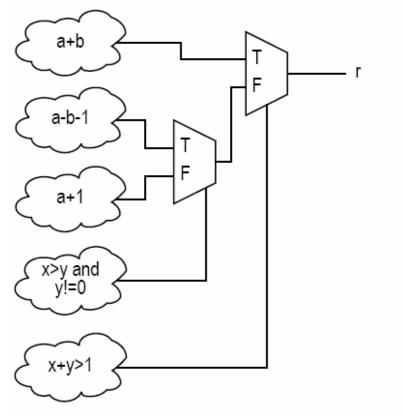

# Conceptual implementation

Syntax:

```

signal_name

<= value_expr_1 when boolean_expr_1 else

value_expr_2 when boolean_expr_2 else

value_expr_3 when boolean_expr_3 else

...

value expr n;</pre>

```

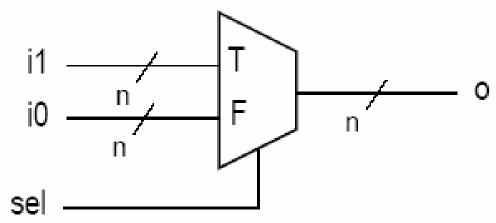

- Evaluation in ascending order

- Achieved by "priority-routing network"

- Top value expression has a "higher priority"

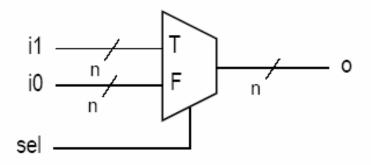

#### 2-to-1 "abstract" mux

- sel has a data type of boolean

- If sel is true, the input from "T" port is connected to output.

- If sel is false, the input from "F" port is connected to output.

RTL Hardware Design

Chapter 4

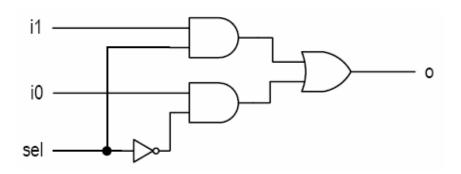

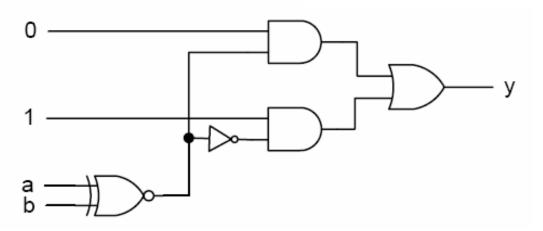

### Detailed implementation examples

#### • 2-to-1 mux

| input | output |

|-------|--------|

| аb    | a=b    |

| 0 0   | 1      |

| 0.1   | 0      |

| 10    | 0      |

| 1 1   | 1      |

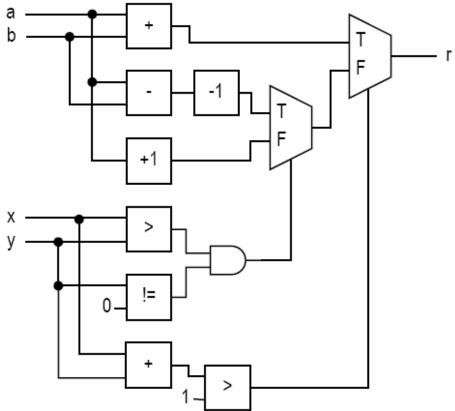

## • E.g.,

```

signal a,b,c,x,y,r: std_logic;

. . .

r <= a when x=y else

b when x>y else

c;

```

```

• E.g.,

```

signal a,b,r: unsigned(7 downto 0);

signal x,y: unsigned(3 downto 0);

. . .

r <= a+b when x+y>1 else

a-b-1 when x>y and y!=0 else

a+1;

Ril naidware Design

Спаріеї 4

# 4. Selected signal assignment statement

- Syntax

- Examples

- Conceptual implementation

- Detailed implementation examples

### Syntax

Simplified syntax: with select expression select signal name <= value expr 1 when choice 1, value expr 2 when choice 2, value\_expr 3 when choice 3, value expr n when choice n;

- select\_expression

- Discrete type or 1-D array

- With finite possible values

- choice\_i

- A value of the data type

- Choices must be

- mutually exclusive

- all inclusive

- others can be used as last choice\_i

### E.g., 4-to-1 mux

```

architecture sel_arch of mux4 is

begin

with s select

x \le a \text{ when "00"},

input

output

b when "01",

S

Х

c when "10",

0.0

а

d when others;

0.1

b

end sel_arch ;

10

С

1 1

d

```

Can "11" be used to replace others?

```

with s select

x <= a when "00",

b when "01",

c when "10",

d when "11";</pre>

```

# E.g., 2-to-2<sup>2</sup> binary decoder

```

architecture sel_arch of decoder4 is

begin

with sel select

x \le "0001" when "00",

"0010" when "01",

input

output

"0100" when "10",

Х

"1000" when others;

0.0

0001

end sel_arch ;

0.1

0010

1.0

0100

1 1

1000

```

## E.g., 4-to-2 priority encoder

| input        | outp | tput   |  |

|--------------|------|--------|--|

| r            | code | active |  |

| 1            | 11   | 1      |  |

| 01           | 10   | 1      |  |

| 0 0 1 -      | 01   | 1      |  |

| $0\ 0\ 0\ 1$ | 00   | 1      |  |

| 0000         | 00   | 0      |  |

• Can we use '-'?

```

with a select

x <= "11" when "1---",

"10" when "01--",

"01" when "001-",

"00" when others;</pre>

```

### E.g., simple ALU

```

architecture sel_arch of simple_alu is

signal sum, diff, inc: std_logic_vector(7 downto 0);

begin

inc <= std_logic_vector(signed(src0)+1);</pre>

sum <= std_logic_vector(signed(src0)+signed(src1));</pre>

diff <= std_logic_vector(signed(src0)-signed(src1));</pre>

with ctrl select

result <= inc

when "000" | "001" | "010" | "011".

when

"100",

sum

diff

when "101",

src0 and src1 when "110".

src0 or src1 when others; input

output

end sel_arch;

ctrl

result

0 - -

src0 + 1

100

src0 + src1

101

src0 - src1

1 1 0

src0 and src1

1 1 1

src0 or src1

```

RTL Hardware Design

Chapter 4

#### E.g., Truth table

```

library ieee;

input

output

use ieee.std_logic_1164.all;

a b

У

entity truth_table is

port (

0.0

0

a,b: in std_logic;

0.1

y: out std_logic

1.0

);

1 1

end truth_table;

architecture a of truth_table is

signal tmp: std_logic_vector(1 downto 0);

begin

tmp <= a & b;

with tmp select

y <= '0' when "00",

'1' when "01",

'1' when "10",

'1' when others; — "11"

end a:

```

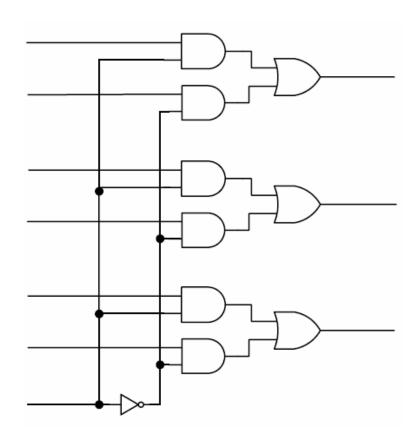

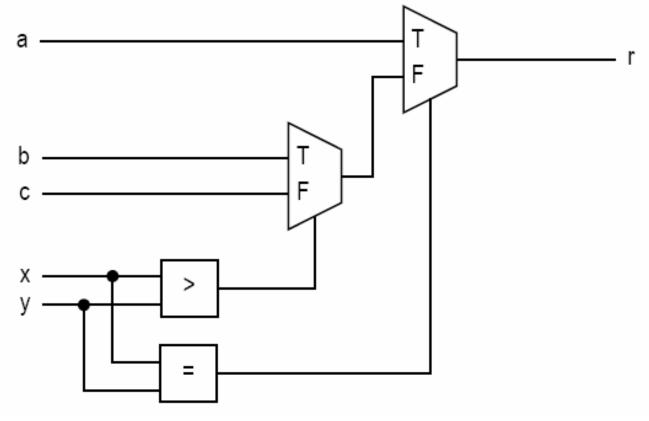

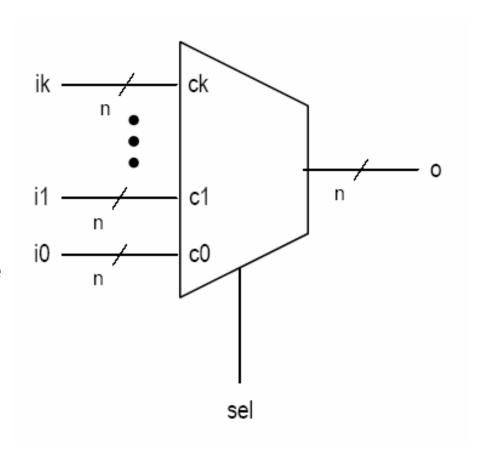

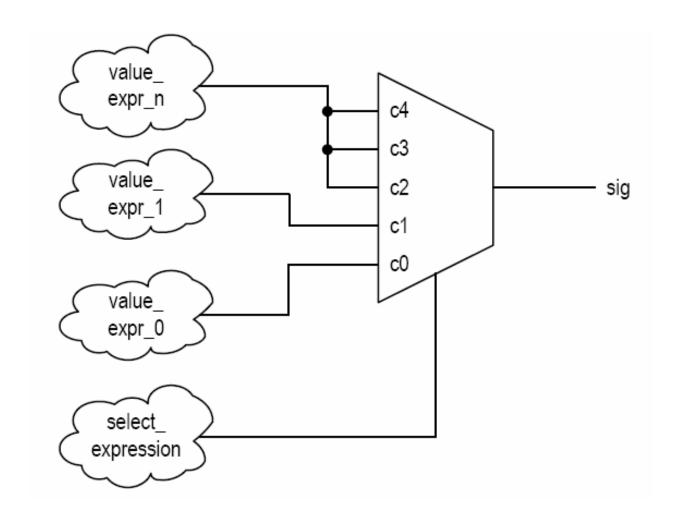

### Conceptual implementation

- Achieved by a multiplexing circuit

- Abstract (k+1)-to-1 multiplexer

- sel is with a data typeof (k+1) values:c0, c1, c2, . . . , ck

select\_expression is with a data type of 5 values: c0, c1, c2, c3, c4

```

with select_expression select

sig <= value_expr_0 when c0,

value_expr_1 when c1,

value_expr_n when others;</pre>

```

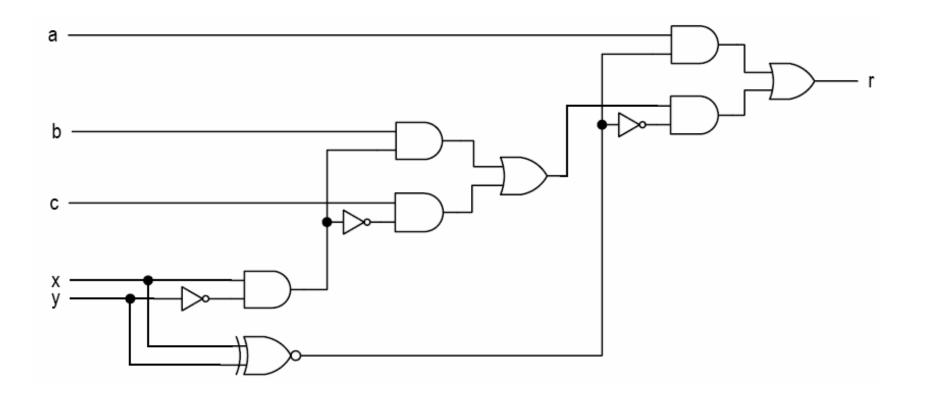

#### Detailed implementation examples

RTL Hardware Design

Chapter 4

RTL Hardware Design

Chapter 4

# 3. Conditional vs. selected signal assignment

- Conversion between conditional vs. selected signal assignment

- Comparison

# From selected assignment to conditional assignment

```

sig <=

value_expr_0 when (sel=c0) else

value_expr_1 when (sel=c1) or (sel=c3) or (sel=c5) else

value_expr_2 when (sel=c2) or (sel=c4) else

value_expr_n;</pre>

```

## From conditional assignment to selected assignment

```

sig <= value_expr_0 when bool_exp_0 else

value_expr_1 when bool_exp_1 else

value_expr_2 when bool_exp_2 else

value_expr_n;</pre>

```

### Comparison

- Selected signal assignment:

- good match for a circuit described by a functional table

- E.g., binary decoder, multiplexer

- Less effective when an input pattern is given a preferential treatment

- Conditional signal assignment:

- good match for a circuit a circuit that needs to give preferential treatment for certain conditions or to prioritize the operations

- E.g., priority encoder

- Can handle complicated conditions. e.g.,

```

pc_next <=

pc_reg + offset when (state=jump and a=b) else

pc_reg + 1 when (state=skip and flag='1') else

. . .</pre>

```

May "over-specify" for a functional table based circuit.

```

b when (s="01") else

c when (s="10") else

d;

x \le c \text{ when } (s="10") \text{ else}

a when (s="00") else

b when (s="01") else

d;

x \le c \text{ when } (s="10") \text{ else}

b when (s="01") else

a when (s="00") else

d;

```