# Using FPGAs With Multiple Cores

### Agenda

- Background: FPGA-based computing

- FPGA computing topologies and scalability

- Hardware acceleration

- Effect of multiple cores on productivity

- Conclusion

- Q&A

# Background: FPGA-Based Computing

#### **Today's FPGA Devices Meet Advanced System Requirements**

- Wide range of fast I/O

- Substantial embedded memory

- High-performance digital signal processing (DSP) blocks

- Abundant logic

- Low-cost FPGA and structured ASIC families

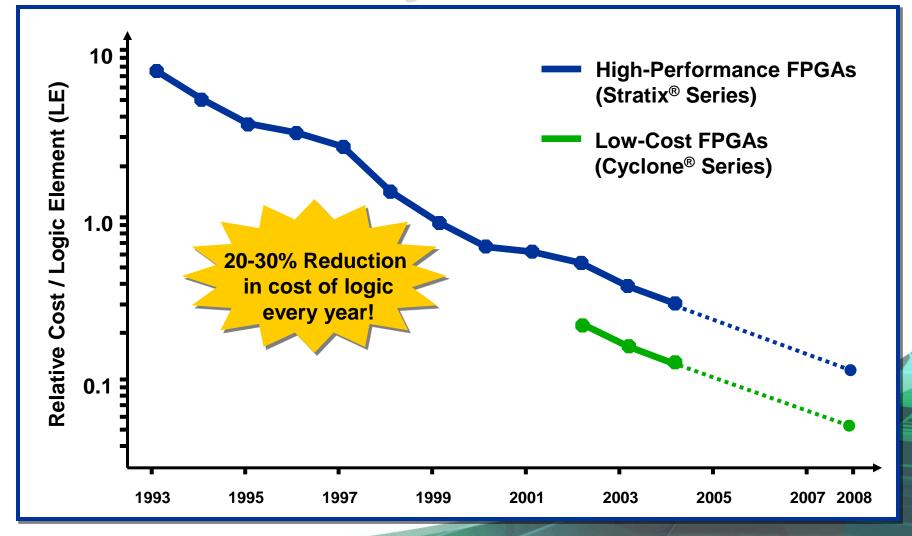

#### **FPGA-Based System Economics**

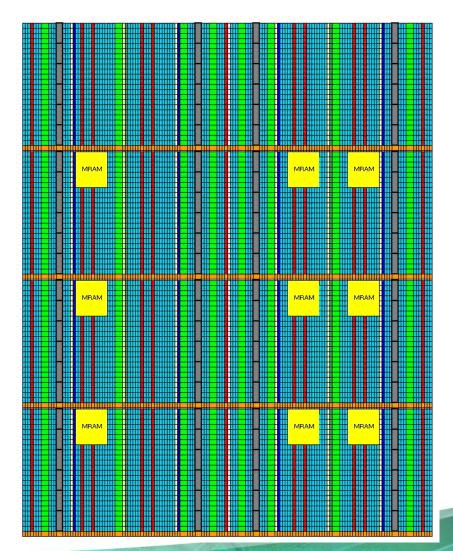

#### Modern FPGAs: Platforms for High-Performance Parallel Architectures

- Example: Altera's Stratix II Family

- First 90-nm high-end FPGA

- TSMC Fab

- Shipped in June 2004

- Rich interconnect fabric

- Up to 180K LEs

- Up to 9 million memory bits

- Up to 96 flexible DSP blocks

- Up to 1,170 high-speed I/O pins

- Many clock trees and phaselocked loops (PLLs)

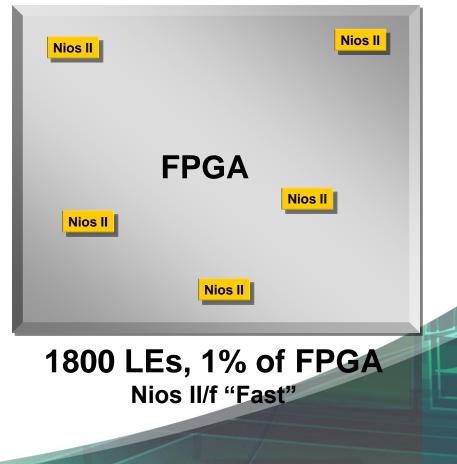

### **Soft-Core CPUs Are Affordable**

Largest Stratix II 180,000 LUTs

Small Cyclone II 4,600 Look-up Tables (LUTs)

600 LEs 13% of FPGA Nios II/e "Economy"

> 35¢ in Lowest-Cost FPGA

### **FPGA = Fast Development**

- Fast time to production

- Prototype and production boards can be the same

- Can accommodate late changes

- Use/reuse intellectual property (IP)

- Fast design cycle

- Develop  $\rightarrow$  synthesize  $\rightarrow$  test

- System-level design tools

- Integration of IP and in-house designs

- Powerful system debug tools – Software and hardware

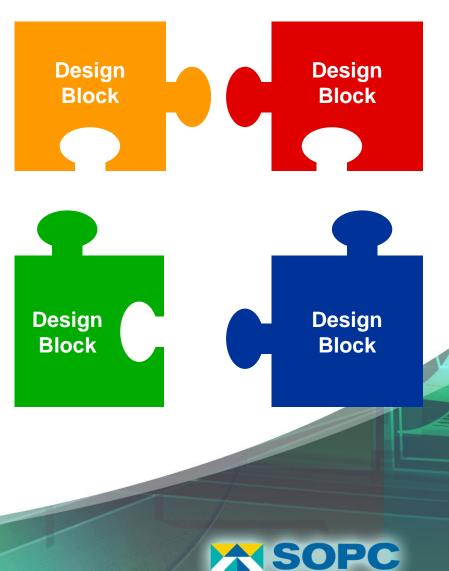

# **Using IP to Increase Productivity**

- Not all blocks are designed with the same interface

- Design for reuse can lead to greater time and cost

- Blocks need integration to create system

#### **SOPC Builder - Automated Integration**

- Generates interconnect between IP blocks

- Supports third party and in-house IP

- Automatically resolves interface issues

- Clock domains

- Bit widths

- Arbitration

- Other issues

## **Updating the System**

SOPC Builder systems can be easily extended

No need to "hack" into existing system

Minimal disruption to the rest of the system

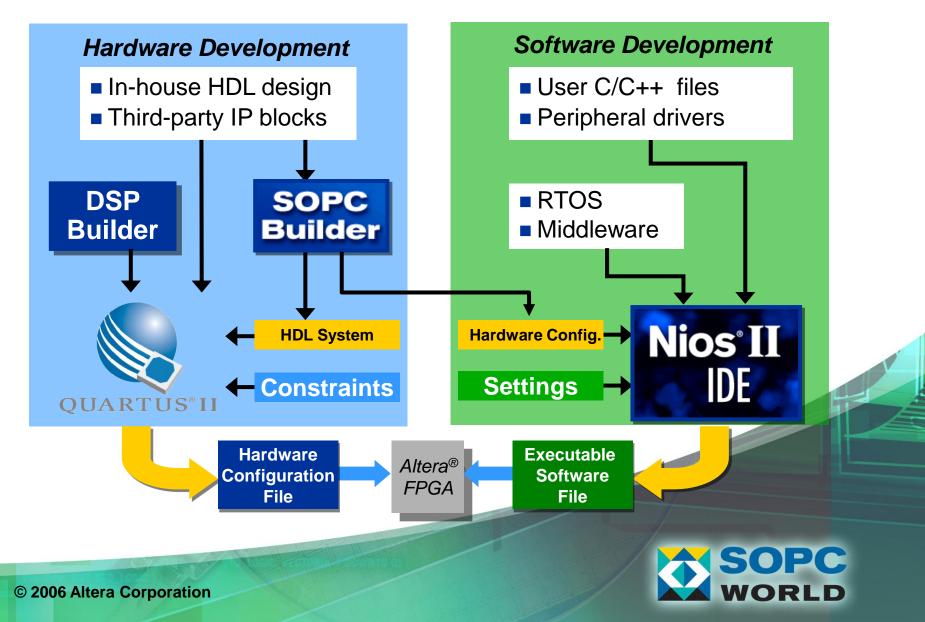

#### **Embedded System Design Flow**

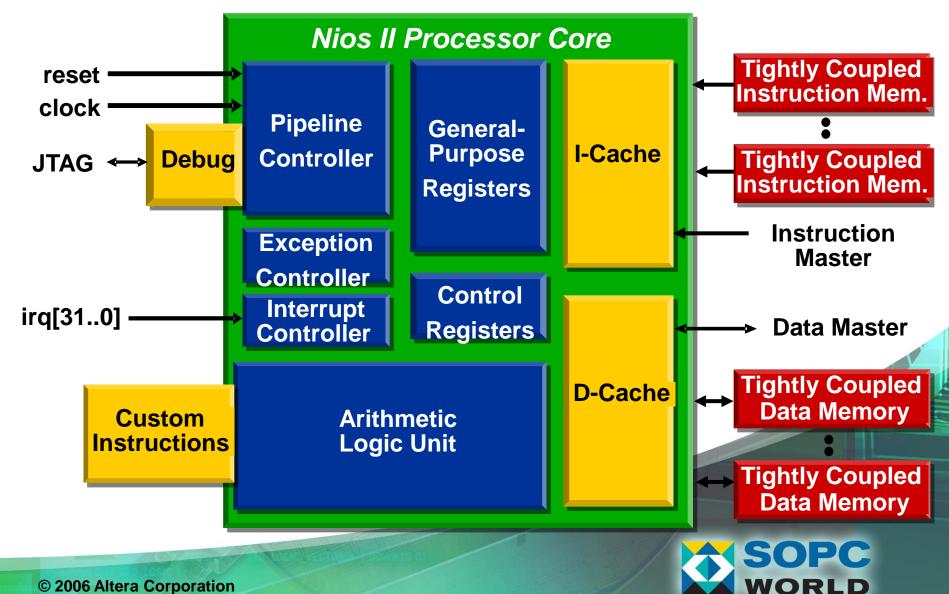

#### **FPGA-Based Soft CPU: Nios II**

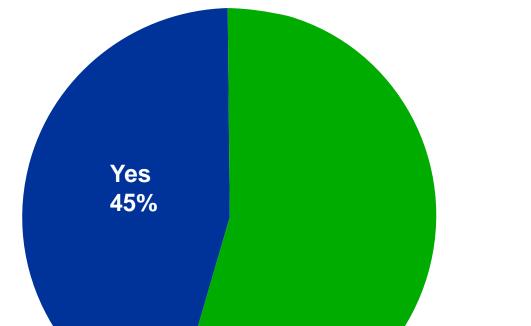

#### **FPGA-Based Soft CPU Usage Trend**

Percent of EE Times embedded systems designers who say they "will likely use a processor inside an FPGA"

Source: CMP 2005 Embedded Market Study

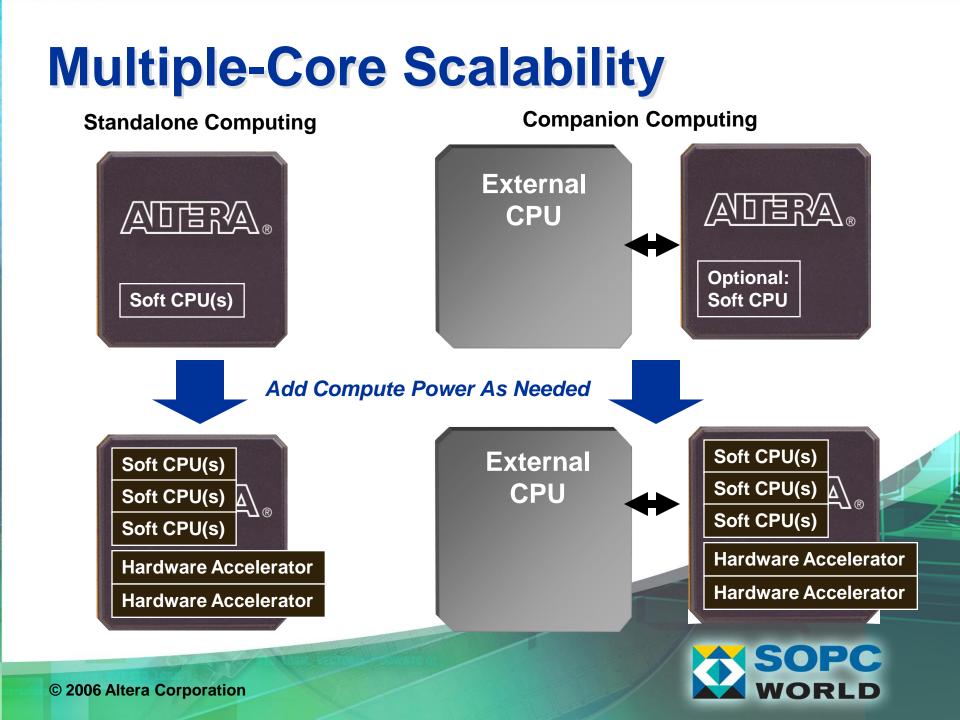

# **FPGA Computing Topologies**

#### **Two FPGA Computing Topologies**

#### Standalone Computing

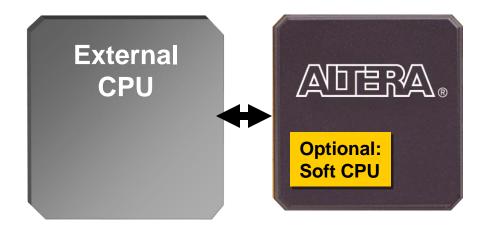

#### **Companion Computing**

#### **Enhancing Your System With FPGAs**

- Peripheral expansion

- Extends life of CPU

- Enhances flexibility

- Avoids costs and risks of using new part

#### **Enhancing Your System With FPGAs**

Peripheral expansion

#### CPU offload

- No increase in clock speed

- Preserves real-time set up

- Low power consumption

- No upgraded components required

- Increases flexibility

#### **Enhancing Your System With FPGAs**

- Peripheral expansion

- CPU offload

- Full system integration

- Very flexible

- Fast development

- No obsolescence issues

- High performance/low cost

#### **Three Ways to Scale Performance**

Hardware

**Accelerators**

Accelerate CPU processing performance with applicationspecific hardware

Add external coprocessing hardware to accelerate data functions Multiprocessor System

Add more processors (internal and/or external) to increase processing power

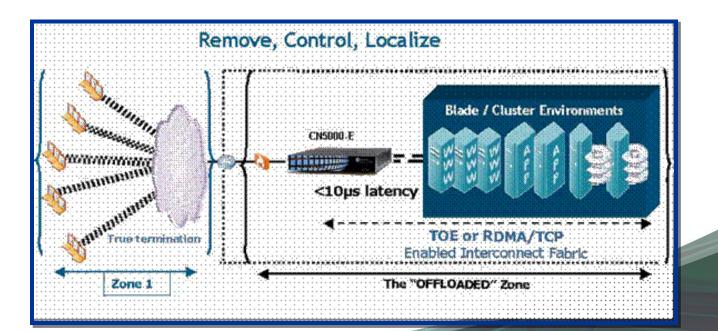

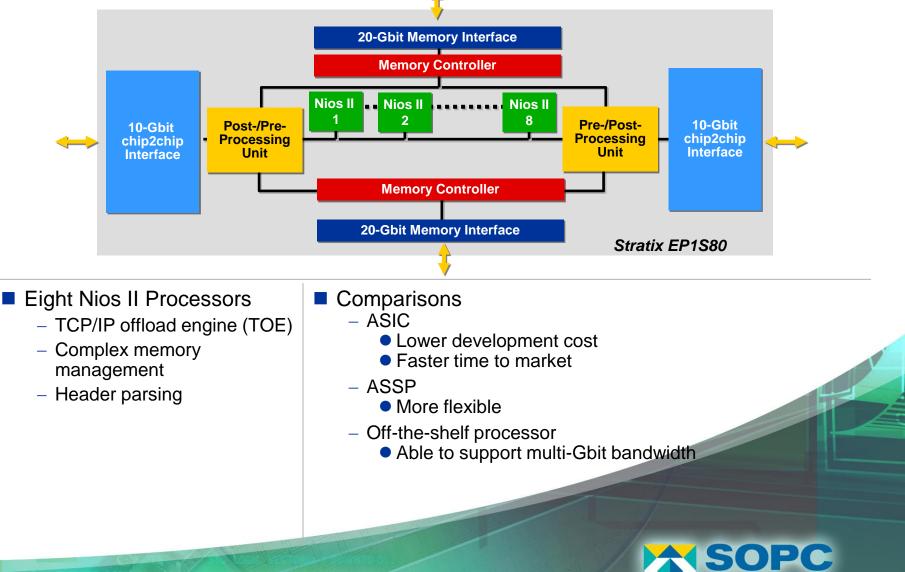

#### Multi-Channel Processing Crescendo Maestro CN-5000E

#### **Application:**

**Application Acceleration Platform**

## **Crescendo Networks**

OP

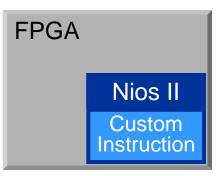

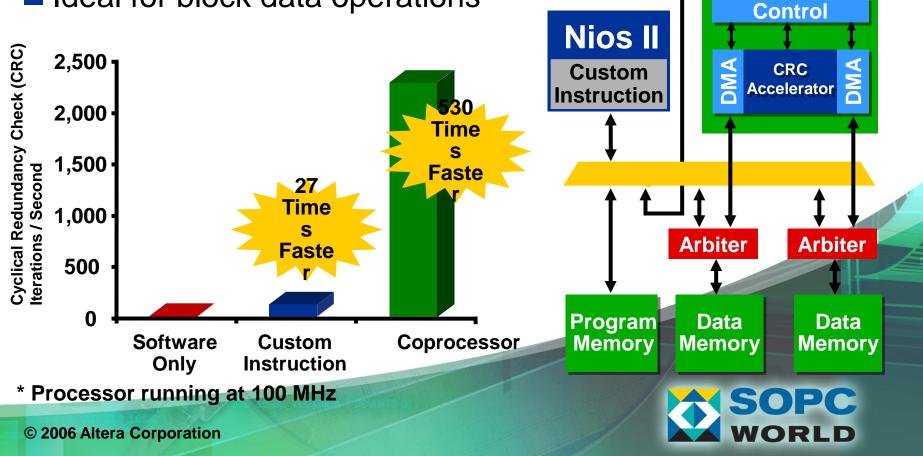

## **Hardware Acceleration**

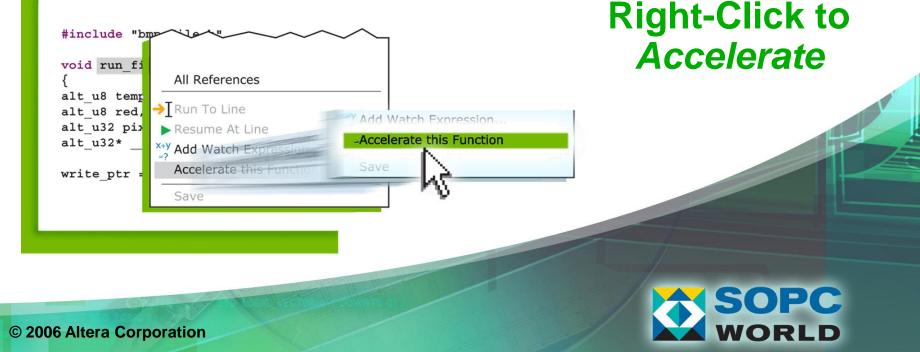

#### Advanced C-to-Hardware Acceleration (C2H) Productivity Tool

- Automates creation and integration of hardware accelerators

- Intuitive user interface streamlines C acceleration

- Uses familiar Nios II Integrated Development Environment (IDE)

- Support for standard ANSI C language

### **Add Hardware Accelerator**

- CPU starts/stops accelerator

- Accelerator fetches data and stores results

- CPU runs application code concurrently

- Ideal for block data operations

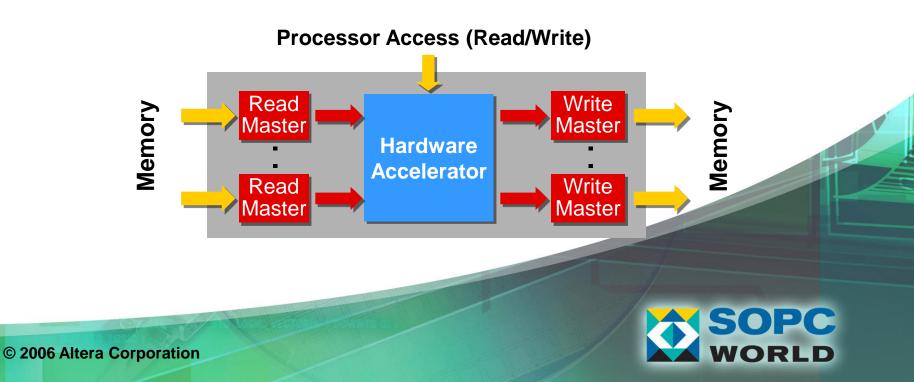

#### **Anatomy of a Hardware Accelerator**

- Multiple Avalon<sup>®</sup> master interfaces to memory

- Accelerator pipelined to match memory latency

- Can sustain extremely high throughput

- Slave interface for CPU control

- Memory mapped registers such as configuration, start, stop, status, etc.

- Software wrapper function

- Controls hardware via slave interface

#### **Adding SOPC Builder Components**

- Import hardware design files

- Map signals to Avalon switch fabric

- Set additional timing parameters

- Add software files (optional)

- Add component information

- Add to SOPC Builder library

#### MyComponent -

| MyComponent 1.0 Settings      |  |  |  |  |  |  |  |

|-------------------------------|--|--|--|--|--|--|--|

| Built on: 2005.08.26.20:20:39 |  |  |  |  |  |  |  |

| Class name: mycomponent       |  |  |  |  |  |  |  |

| Class version: 1.0            |  |  |  |  |  |  |  |

| Component name: MyComponent   |  |  |  |  |  |  |  |

| Component Group: User Logic   |  |  |  |  |  |  |  |

| Parameters                    |  |  |  |  |  |  |  |

| BLOCK_SIZE: 16                |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |

| ERROR_CODE: Error!!           |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |

| 🔩 Component Editor - My Component                                   |                   |           |      |           |            |    |  |  |

|---------------------------------------------------------------------|-------------------|-----------|------|-----------|------------|----|--|--|

| _                                                                   | <u>T</u> emplates |           |      |           |            |    |  |  |

| Introduction HDL Files Signals Interfaces SW Files Component Wizard |                   |           |      |           |            |    |  |  |

|                                                                     |                   |           |      |           |            |    |  |  |

|                                                                     |                   | File Name | Info | Synthesis | Simulation |    |  |  |

|                                                                     | State State       |           |      |           | SC         | PC |  |  |

## **Performance Comparison**

#### Mandlebrot algorithm

- Pentium M running 1,600 MHz, entirely out of cache (best case)

- Cyclone II system running Nios II processor at 75 MHz with acceleration blocks

|                             | Floating-<br>Point<br>Software | Integer<br>Software | Accelerator<br>Hardware | Direct<br>Memory<br>Access<br>(DMA) I/O<br>Offload<br>Hardware |

|-----------------------------|--------------------------------|---------------------|-------------------------|----------------------------------------------------------------|

| Pentium at<br>1,600 MHz     | 30 ms                          | 110 ms              | NA                      | NA                                                             |

| Pentium at 75 MHz           | 640 ms                         | 2347 ms             | NA                      | NA                                                             |

| Nios Processor at 75<br>MHz | 351,789 ms                     | 243,017 ms          | 211 ms                  | 35 ms                                                          |

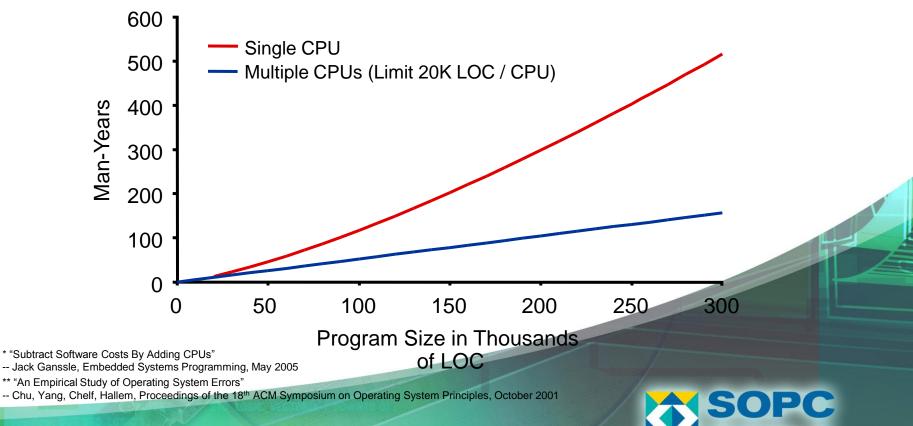

# Effect of Multiple Cores on Productivity

#### **Multiple Cores Drive Team Productivity**

- Each processor runs fewer lines of code

- Smaller projects are faster to develop

- "Double the lines of code (LOC) and multiply man-months by four" \*

- Improves reliability and maintainability

- Large function error rates 2X to 6X higher than smaller routines \*\*

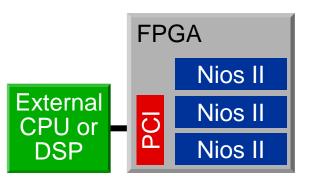

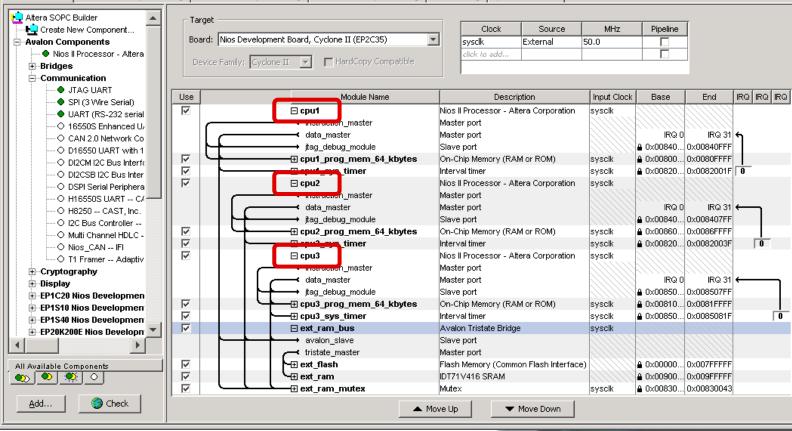

# Multiprocessor System Design Made Easy

- Building multiple-CPU systems with SOPC Builder

- As many Nios II CPUs as you like

- Communicate via shared memory mailbox

- Share hardware resources with mutex core

- Software development:

- Integrated drive electronics with multiprocessor debug support

- Software drivers for mailbox and mutex

- Enhanced tool support from Lauterbach

Example designs and application notes

## **Nios II Multiprocessor System**

#### 🗖 Altera SOPC Builder - std\_1s40

File Module System View Tools Help

System Contents Nios II More "cpu1" Settings Nios II More "cpu2" Settings Nios II More "cpu3" Settings Board Settings System Generation

#### **Benefits of Multiprocessor Design** Can increase performance More work per clock cycle Can scale system design Add CPU when required Can reduce cost - External processor upgrade not required Can simplify software development

## Conclusion

### Conclusion

FPGAs can be viewed as a flexible, scalable computing platform

- FPGAs support general and specialized computing cores

- FPGA-based soft CPU cores are maturing, moving into mainstream

- FPGAs provide flexible way for leveraging productivity advantages of multi-core computing

### **Call for Actions**

#### Please download Nios II Embedded Processor

- http://www.altera.com/download

Please visit SOPC World Booth for Demos

## Thank You Q & A