![]()

작성일: 2014.06.23

![]()

최근 레이더가 주차 보조 및 차선 이탈 경고 등을 위해 고가 차량용 플랫폼에 적용되기 시작했다. 이들 애플리케이션은 능동 충돌 방지 및 적응형 크루즈 컨트롤 등을 포함하며 지속적으로 확대될 것이다. 거리, 속도, 방향을 결정하기 위한 레이더 신호의 디지털 신호 처리 기능은 SoC FPGA를 사용하는 것이 이상적이다.

많은 레이더 시스템이 펄스-도플러(pulse-Doppler) 방식을 채용하고 있는데, 이는 전송기가 짧은 주기로 동작한 후 시스템이 다음 전송 펄스까지 수신 모드로 전환된다. 레이더가 돌아오기 때문에 반사 신호들이 일관성 있게 처리되어 거리와 감지된 대상의 상대적인 동작을 추출할 수 있다.

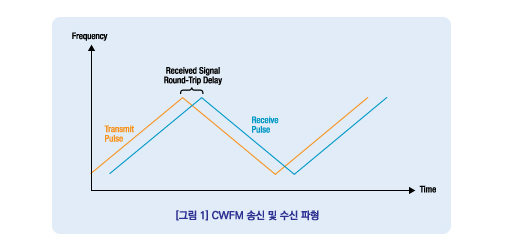

차량용 레이더의 경우, 거리가 수 미터에서 수백 미터로 짧다. 2미터 거리의 경우, 레이더 펄스의 왕복 전송 시간이 13ns이다. 이 짧은 거리로 인해 송신기와 수신기가 동시에 동작해야만 하기 때문에 각각 안테나가 필요하다. 주기가 일반적으로 작기 때문에 이 비율이 전체 송신 전력을 제한한다. 반면, 전력은 감지 거리를 제한한다. 그 대신에 CWFM(continuous wave frequency modulated)으로 알려진 레이더 방식을 채용할 수 있다. CWFM은 펄스를 전송하지도, 복귀 신호 또는 레이더 에코(radar echo)를 모니터링하지 않는다. 대신에 반송 주파수(carrier frequency)를 지속적으로 전송한다. 유용한 정보를 연속 복귀 에코로부터 추출하기 위해서 다음 그림 1에 나타낸 바와 같이 반송 주파수가 시간이 경과함에 따라 높아지고 낮아진다. 송신기와 수신기 모두 지속적으로 동작한다.

CWFM에서 거리는 송신 주파수와 순간 수신 주파수와의 차이 또는 델타를 측정하여 얻을 수 있다. 송신 사이클의 주파수가 높아지는 영역 동안, 수신 주파수가 시간 지연에 따라 송신 주파수보다 일정 정도 낮아진다. 이러한 주파수 차이 또는 오프셋은 왕복 지연 시간과 비례하며, 거리를 측정할 수 있는 방법을 제공한다. 이 관찰된 주파수 오프셋은 수신기 거리 복귀 신호는 제공하지만, 앞에서 다가오는 차량, 동일한 방향으로 주행하는 차량, 유사한 거리 내에 있는 고정 물체 등을 구별하는 데에는 사용할 수 없다. 이를 구별하기 위해서 복귀 신호의 도플러 주파수 천이(Doppler frequency shift)을 활용해야만 한다.

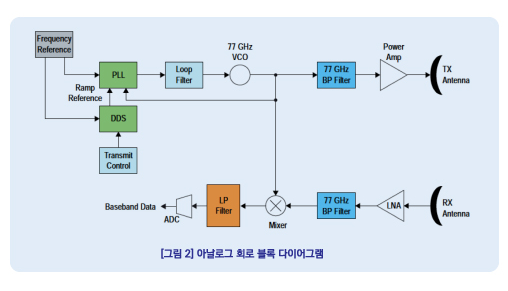

CWFM 레이더 아키텍처의 장점은 아날로그와 디지털 구현 방법 모두가 간단하다는 것이다. 아날로그 측면에서 표준 레퍼런스 크리스털을 사용하여 DDS(direct digital synthesizer)를 통해 송신기를 구현할 수 있다. DDS는 PLL(phased-locked loop)을 위한 아날로그 주파수 램프 레퍼런스를 생성하여 필요한 전송 주파수 변조를 생성할 수 있다. 예를 들어, PLL이 1000의 디바이더를 사용한다면, 본고의 예제에서는 레퍼런스는 77MH의 중앙 주파수와 5MHz 주파수 램프를 가지게 된다. 이 아날로그 램프 신호는 77GHz 오실레이터를 관리하는 PLL의 레퍼런스를 구동한다. 회로의 오실레이터 출력은 증폭되어 77GHz의 중앙 주파수를 통해 500MHz까지 상승/하강하는 CW(continuous wave) 신호를 생성한다. 77GHz의 필터링 및 매칭 회로는 하이-엡실론 R 유전체 회로 카드로 에칭된 수동 부품들을 통해 구성될 수 있으며, 필요한 부품을 최소화할 수 있다. 그림 2는 아날로그 회로 블록 다이어그램이다.

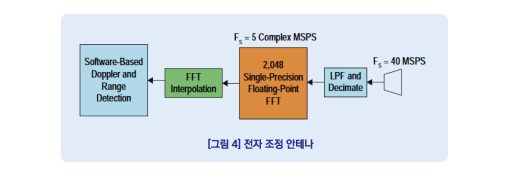

수신기의 경우, 프론트 엔드는 아날로그 믹서 이후에 필터링과 LNA(low-noise amplifier)를 필요로 한다. 이 믹서는 램핑 송신 신호와 함께 77GHz 수신 신호를 하향변환시켜 해당 순간의 송신과 수신 파형의 차이를 포함하는 기저 신호를 출력한다. 거리 및 타깃 복귀 신호의 도플러 천이에 따라서 고정 주파수를 관찰하기 때문에 램핑은 제거된다. 믹서의 출력은 최대 거리 조건에서 최대 ±2MHz의 저주파수가 된다. 베이스밴드 신호는 (주파수가 낮아지는 기간 동안) 모두 높아지거나 (주파수가 높아지는 기간 동안) 모두 낮아지는 주파수로 구성되기 때문에 단일 저대역 필터 및 ADC 다음에 믹서를 사용하면 충분하다. 베이스밴드 입력을 위한 ADC는 최소 5MSPS 조건으로 동작해야만 나이퀴스트 기준(Nyquist criterion)을 충족할 수 있다. 대신 8:1 디지털 데시메이션 필터(digital decimation filter) 다음에 40MSPS의 8x 샘플링 주파수를 사용할 경우, 약 3bit의 추가적인 해상도를 달성할 수 있다.

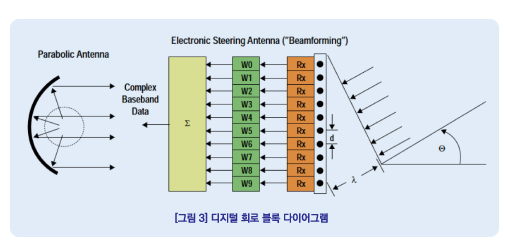

디지털 필터는 16bit 입력 샘플을 사용하여 160MHz 속도로 동작할 수 있으며, 5MHz 조건에서 샘플들을 출력할 수 있지만 24bit로 반올림된다. 신호 처리의 다음 단계는 보간 회로(interpolation circuit) 이후에 FFT를 사용하여 주파수를 식별하는 것이다. FFT의 특성은 처리 단계를 거침에 따라서 데이터 정밀도가 증가한다는 것이다. 본고에서는 2,048 포인트 FFT를 가정하는데, 이는 데이터 손실을 방지하기 위해서 잠재적으로 최대 10개의 추가 비트 정밀도를 요구할 수 있다. 하지만, 단정밀도 부동소수점 처리 기능을 구현하여 이러한 비트 증가를 방지할 수 있다. 전체 24bit 가수 정밀도(mantissa precision)(23bit 과 사인 bit)를 FFT를 통해 보존할 수 있으며, 타깃 복귀 신호의 100+ dB 동적 범위를 간단하게 수용할 수 있다. 그림 3은 디지털 회로 블록 다이어그램이다.

부동소수점 FFT 회로는 또한 10MSPS 조건에서 복소 데이터를 처리함으로써 160MHz로 구현될 것이다. 완벽한 부동소수점 회로를 생성하는 것뿐만 아니라 클록 속도가 데이터 속도보다 높을 경우에 데이터 경로를 "폴딩(folding)"할 수 있기 때문에 로직 및 DSP 블록 자원 뿐만아니라 전력소모를 절약할 수 있다. 타이밍 클로져 프로세스를 자동화하는 DSP Builder 툴을 사용하여 이러한 최적화를 알테라의 Cyclone V SoC FPGA에서 모두 구현할 수 있다. 저비용 Cyclone V SoC FPGA는 18 x 19 및 27 x 27 곱셈기 크기를 모두 지원하는 DSP 블록을 제공한다. 상대적으로 큰 27 x 27 곱셈기 크기는 부동소수점 설계에 사용하기에 이상적이다. 감지 처리 기능은 온-칩 ARM Cortex-A9 마이크로프로세서 중 하나를 사용하여 수행된다.

지금까지 설명한 레이더 시스템은 거리와 속도 또는 목표를 감지할 수 있지만, 목표의 방향과 관련된 정보는 전혀 제공하지 않는다. 시스템이 레이더 송신 또는 수신 안테나의 방향성을 스윕하거나 조정할 수 있다면 방향성을 결정할 수 있다. 차량용 레이터의 경우, 안테나의 선형 배열 또는 안테나의 라인이 안테나의 방위각(면대면)을 조정할 수 있다. 수신 신호의 디지털 처리 기능으로 인해 수신 방향을 조정할 수 있다. 각 수신기는 개별적으로 수신 신호의 위상을 변화시켜야만 한다.

어레이 안테나는 필요한 방향으로 안테나의 메인 로브(main lobe)를 조정할 수 있다. 각 안테나 요소는 지연 또는 위상 조정 기능을 가지고 있어야만 하며, 이러한 조정 후에 모든 요소들이 신호에 대해 공통 위상을 가져야 한다. 만약 각 θ = 0이면, 모든 요소들이 신호를 동시에 수신하게 되며, 위상 조정이 전혀 필요하지 않다. 각도가 0이 아닐 경우, 각 요소들은 그림 4에 나타낸 바와 같이 안테나 어레이에 대해 파형을 조정하기 위해서 지연 특성을 가지게 된다.

디지털적으로 각 안테나 노드의 ADC의 각 입력 세트는 위상에서 지연되어야만 한다. 이 지연은 N 수신 노드 각각에 대해 N 독립 복소 계수 Wi를 사용하는 복소 곱셈기(complex multiplier)에 의해 구현된다. Cyclone V SoC FPGA의 DSP 블록은 이 기능에 특히 적합하며, 1개의 DSP 블록이 완벽한 고속 복소 곱셈기를 구현할 수 있다. 제어 프로세서가 N 복소 계수를 주기적으로 업데이트하여 수신 안테나를 "스윕(sweep)"하고 목표 복귀 진폭(target return amplitude)의 변화를 모니터링한다. 예를 들어, 크기 4에서 16까지의 N을 위한 빔형성(beamforming)을 지원하는 데 필요한 추가적인 FPGA DSP 블록과 로직 자원은 상당히 작다.

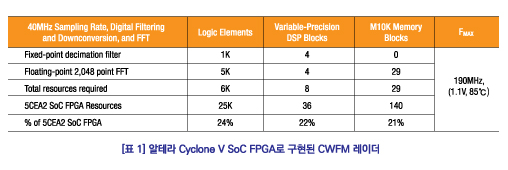

표 1은 알테라의 Quartus II 소프트웨어가 제공한 FPGA 자원 예상을 정리한 것이다. CWFM 설계를 알테라의 최저 비용 SoC FPGA로 간편하게 구현할 수 있다. 이러한 방법을 통해, 차량용 레이더 애플리케이션을 신속하게 출시할 수 있다.

![]()